元旦快乐,更新一个Linux开发版的绘制过程。

1 什么是高速PCB

高速PCB(Printed Circuit Board)指的是用于高速信号传输的电路板,通常用于频率较高或数据速率较快的电子系统中,如通信设备、计算机、服务器和高速存储。其设计关注信号完整性、电磁兼容性和传输线效应,需精确控制阻抗、层叠结构和走线布局,以减少信号衰减、串扰和反射。高速PCB设计还会考虑材料选择和电源完整性,确保系统在高速工作条件下的稳定性和可靠性。

2 硬件篇

2.1 原理图绘制

天下板子一大抄,因为都是模块化好的东西,也不能自己随意修改引脚,不然就是给软件挖坑。

2.2 层叠设计与阻抗

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。

2.3 PCB绘制

2.3.1 器件介绍

PCB的绘制并不是随意摆放画线,尤其是高速PCB,当然低速的不必要讲究那么多。为此这里主要梳理了常见的模块器件的介绍,布局布线要求。

链接区域(DDR emmc HDMI RJ45 SD USB WIFI+BT 晶体 PMU)

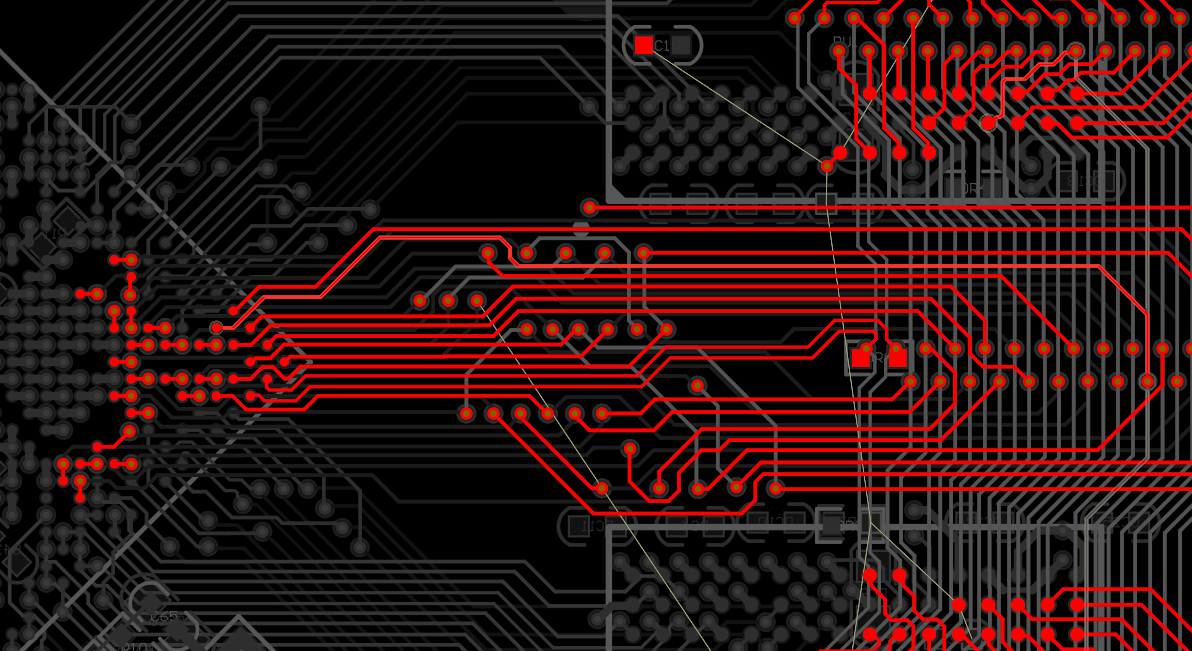

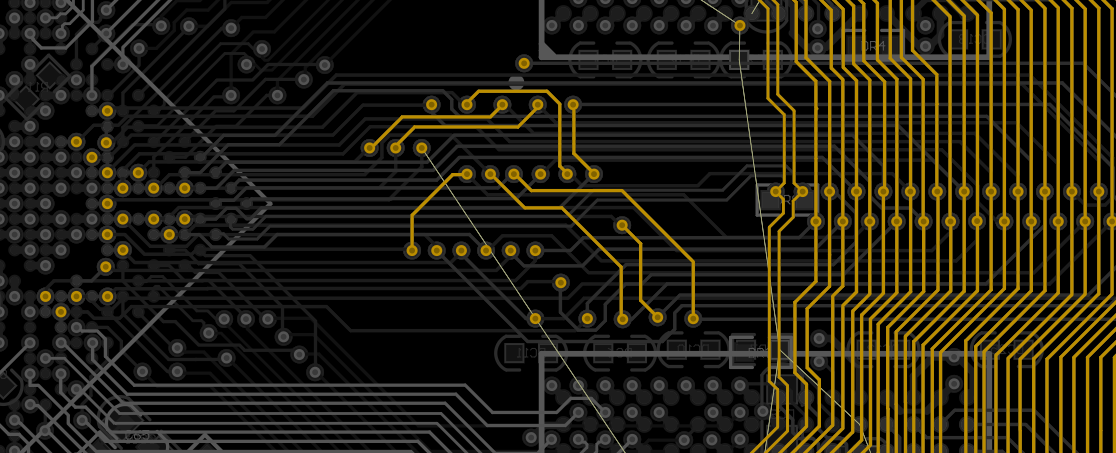

2.3.2 设计过程

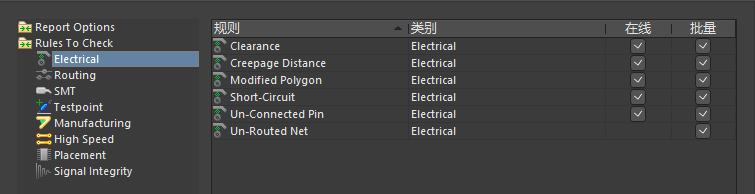

1.把不需要的DRC检测去除,只留电路的DRC。

2.调整器件位号大小和位置,高10mil,宽2mil,器件位号放置器件中心。

3.设计禁布区,板边预留10mil,防止器件和线路靠近边缘损坏。

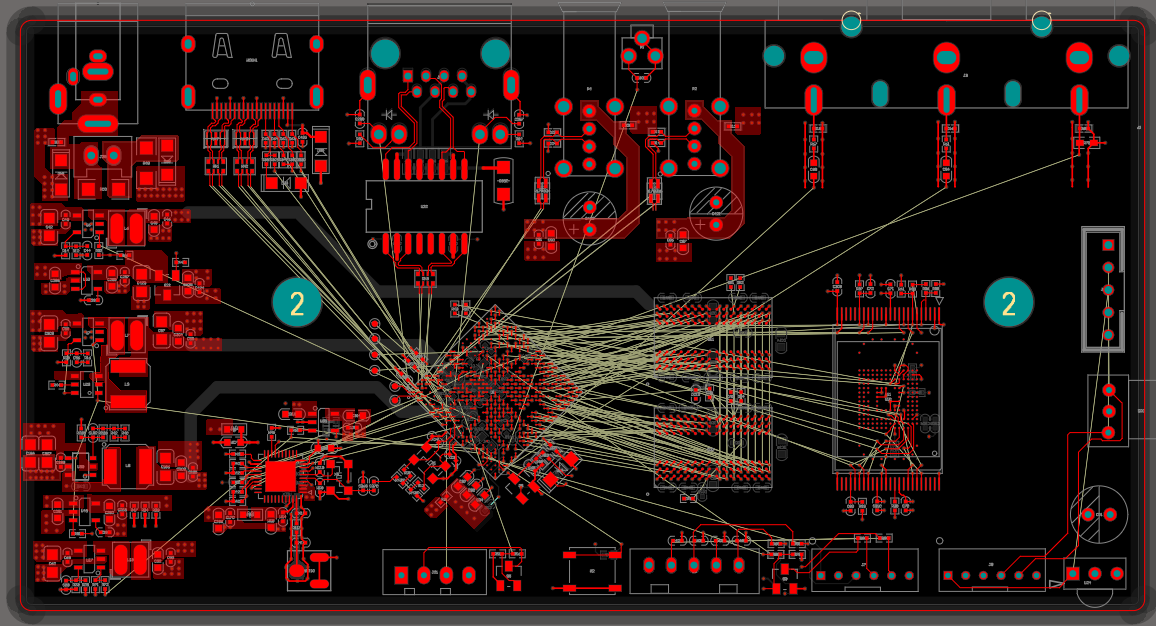

4.各个模块预布局。固定器件优先布局,模块相关的器件放置旁边。

5.对于容易受到干扰(射频和存储器)和容易干扰别人的模块(电源)需要加屏蔽罩。

6.对各个模块进行布局。然后对电阻电容等间距,对齐。

7.对板子进行层数判断,以及阻抗进行计算,内缩20H,20倍介质厚度。常用:电源内缩地40mil,GND内缩20mil,POWER内缩60mil。重要信号线走在第三层。

8.设置class,规则。具体可看下面的注意事项。

9.主控与ddr的扇出和滤波电容摆放。其余器件进行扇孔,短线直接连接,长线打孔,电源打孔。

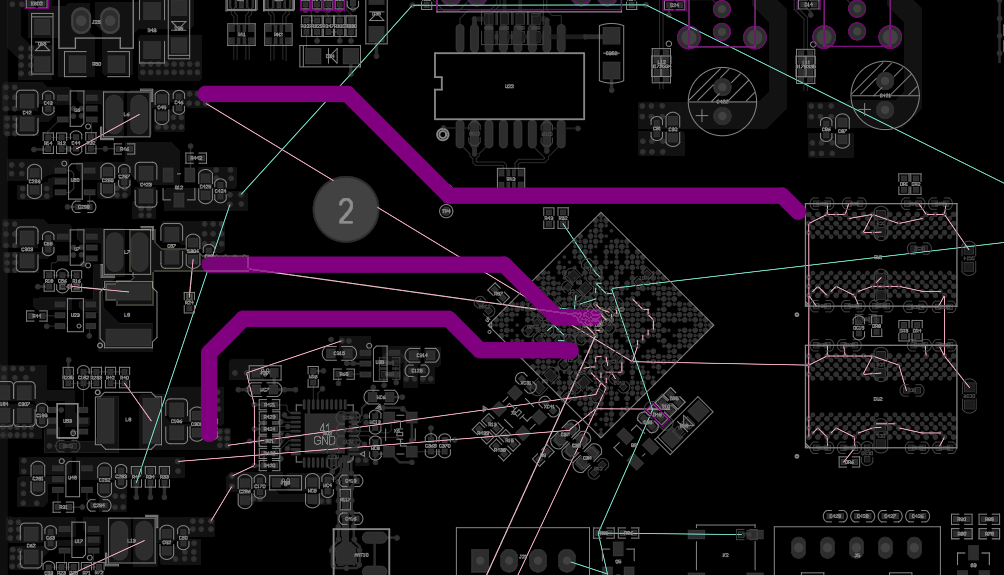

10.电源模块处理,主干道铺铜。整板电源流向分析与规划。对于分散的电源,可以考虑整版电源层。

11.对主控外围器件扇孔。隐藏信号线,可以看到只有小部分线了。

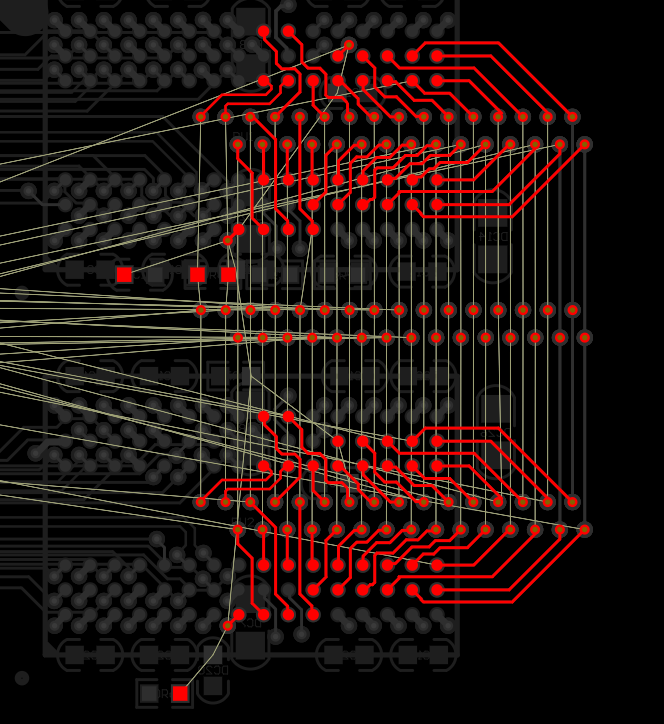

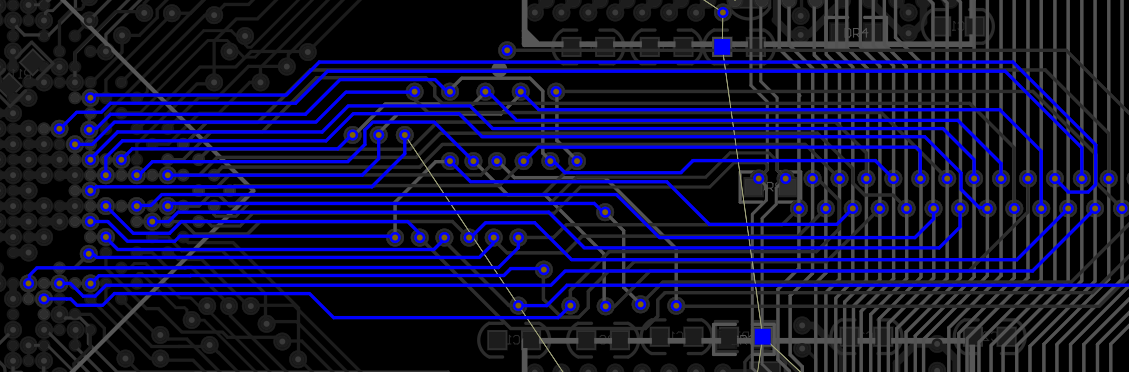

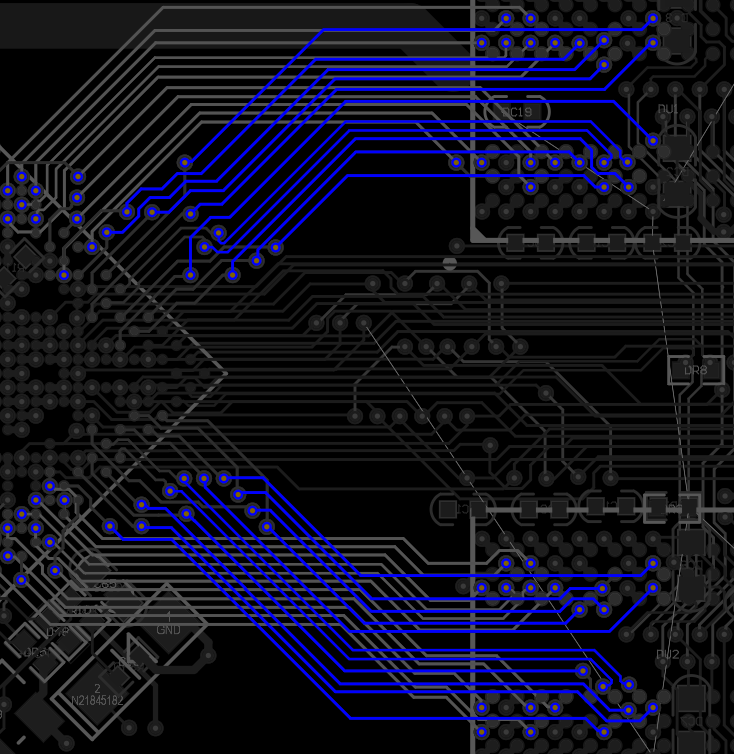

12.布线先从板子最密的区域开始,先从DDR开始布线。设置分组,然后数据线,地址线布线。

13.flash和emmc的拓扑结构,先连到flash,在连到emmc。

14.其余器件进行走线,然后是一些杂线。

15.电源的处理:大电源采用平面分割处理,小电源采用走线(信号层)处理。GND最后处理。

2.3.3 注意事项!!!(重要)

预布局注意事项:

- 预布局时,可以先创建PWR类,把电源和GND的飞线全部隐藏。只打开主控的飞线。

- 固定器件优先摆放。其次调整主控位置,其余器件按照飞线方向摆放,尽量减少交叉。

- 还需要考虑核心电源走向,高频(ddr和射频)部分也需要与电源尽量远离。

- DDR需要等长,所以要和主控预留一定的空间。

- 可以参考别人的芯片布局,运用框架思维合理摆放,然后再局部的布局。

阻抗计算注意事项:

- 如果掌握不了,可以按照通用线宽,然后让厂家进行调整。

- 首先确定板子的材质和厚度,比如1.6mm厚的6层板,需要知道PP片厚度,内外层铜厚和芯板的厚度,然后根据材质,相对应的介电系数来计算阻抗,各个厂家所用的PP片不同,所以具体情况需要具体分析。

- 可以使用嘉立创的免费方案,计算也快,嘉立创外层铜厚1盎司,内层0.5盎司。

- 各个模块具体阻抗参考:

- emmc:单端50Ω,没有差分信号。

- DDR:单端50Ω,差分100Ω。

- HDMI:100Ω差分阻抗 4对差分线。

- USB(USB2.0,USB3.0,Typec):90Ω差分阻抗,一对差分线。

- 网口:100Ω差分阻抗, 百兆网口两对差分,千兆网络四队差分。

- 射频天线:单端50Ω。

- 90%都是100Ω差分阻抗,除了USB是90Ω差分阻抗。

知道阻抗后就可以规定走线的线宽。

class,规则注意事项:

- class主要使用网络类和差分类。

- 网络类

- PWR网络—加粗线宽(10-20mil)

- AV模拟信号-12mil

- ddr

- 数据线x2

- 地址

- flash

- 差分类

- HDMI:4对差分

- USB:1对差分

- DDR:3对差分 DM(数据掩码),DQS(数据锁存),SCK(时钟)。

- 网络:2对差分,一队TX,一对RX。

- 规则添加:

- 最小线宽可以改为5mil。

- 电源线宽加粗,8-100mil。信号线首选5mil,然后根据阻抗来选择线宽。

- 过孔规则: 盘 = 2 X 孔 ±2mil 过孔孔径8mil 过孔直径14mil

- 阻焊(SolderMaskExpansion)规则: 2.5mil

- 铺铜规则:

- (PlaneConnect):全连接。

- 反焊盘(PlaneClearance):设置7mil。

- 正片层铺铜(PolygonConnect) 考虑载流用全连接,考虑焊接用十字连接

- 各个模块有其具体规则,这里不在赘述。

嘉立创六层免费打板最小线宽3.5mil,最小孔径/外径0.2、0.45mm;

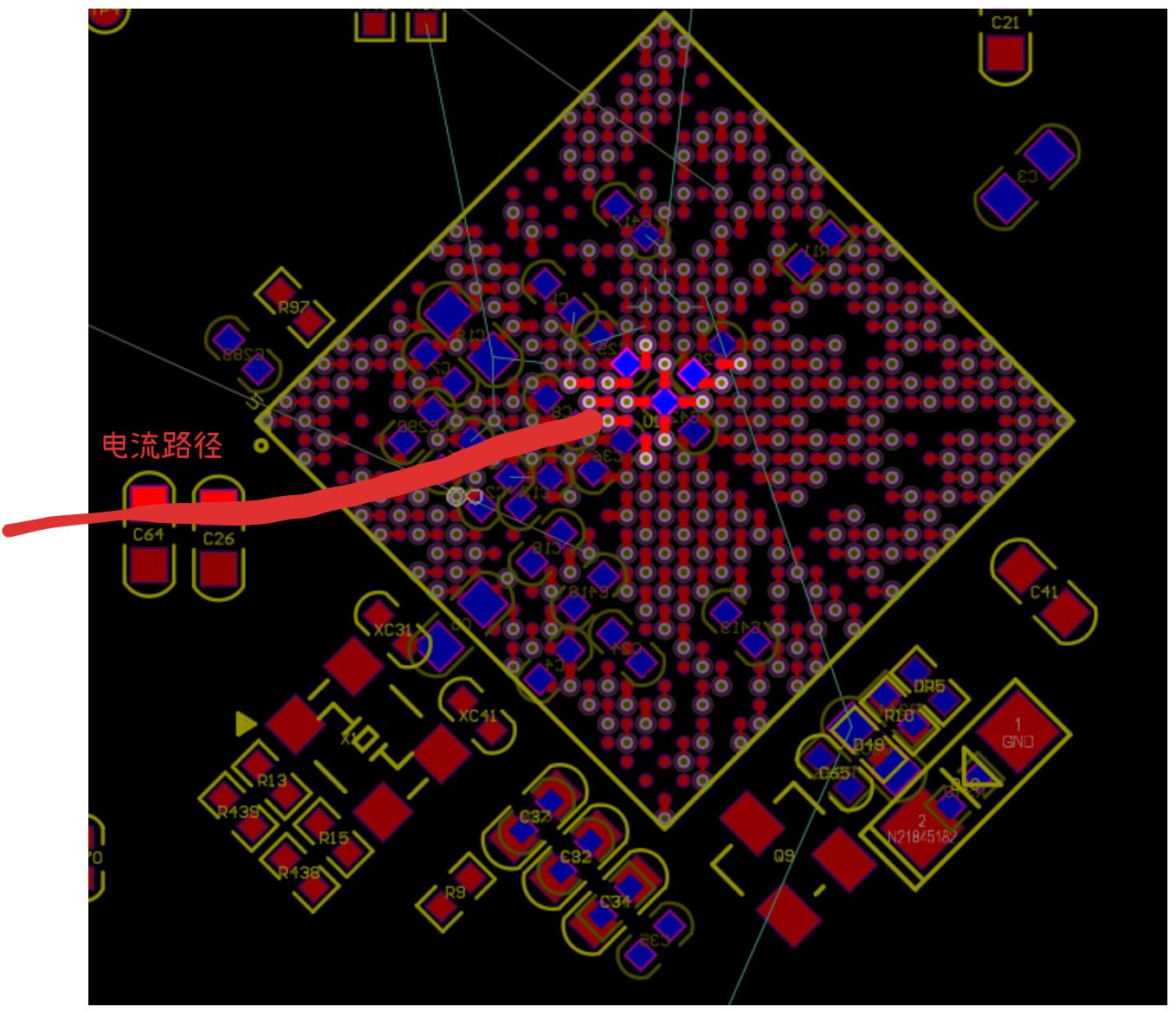

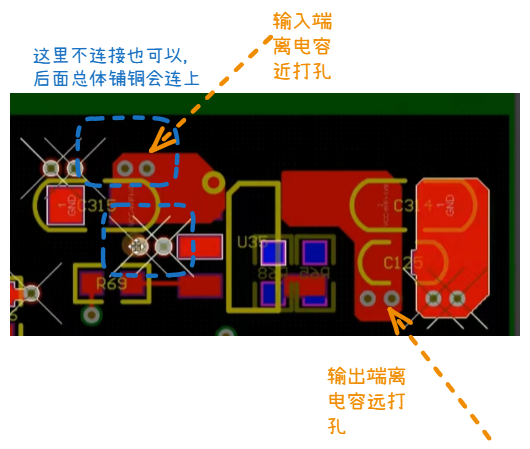

BGA扇出,放置滤波电容注意事项:

- 扇出的过孔位于四个焊盘中间,可以手工或者软件扇出。

- 滤波电容优先摆放,放置滤波电容时需要平均分配,大电容滤除低频部分,小电容滤除高频部分。小电容优先靠近引脚摆放,大电容归中摆放。

- 可以调整过孔位置,合孔来摆放器件。电阻可以拉远一点摆放。先放后调整。

- 小滤波电容塞满后,在放大滤波电容,若是塞不下,就放在电源路径上。

- 注意电源流向,放置stub。

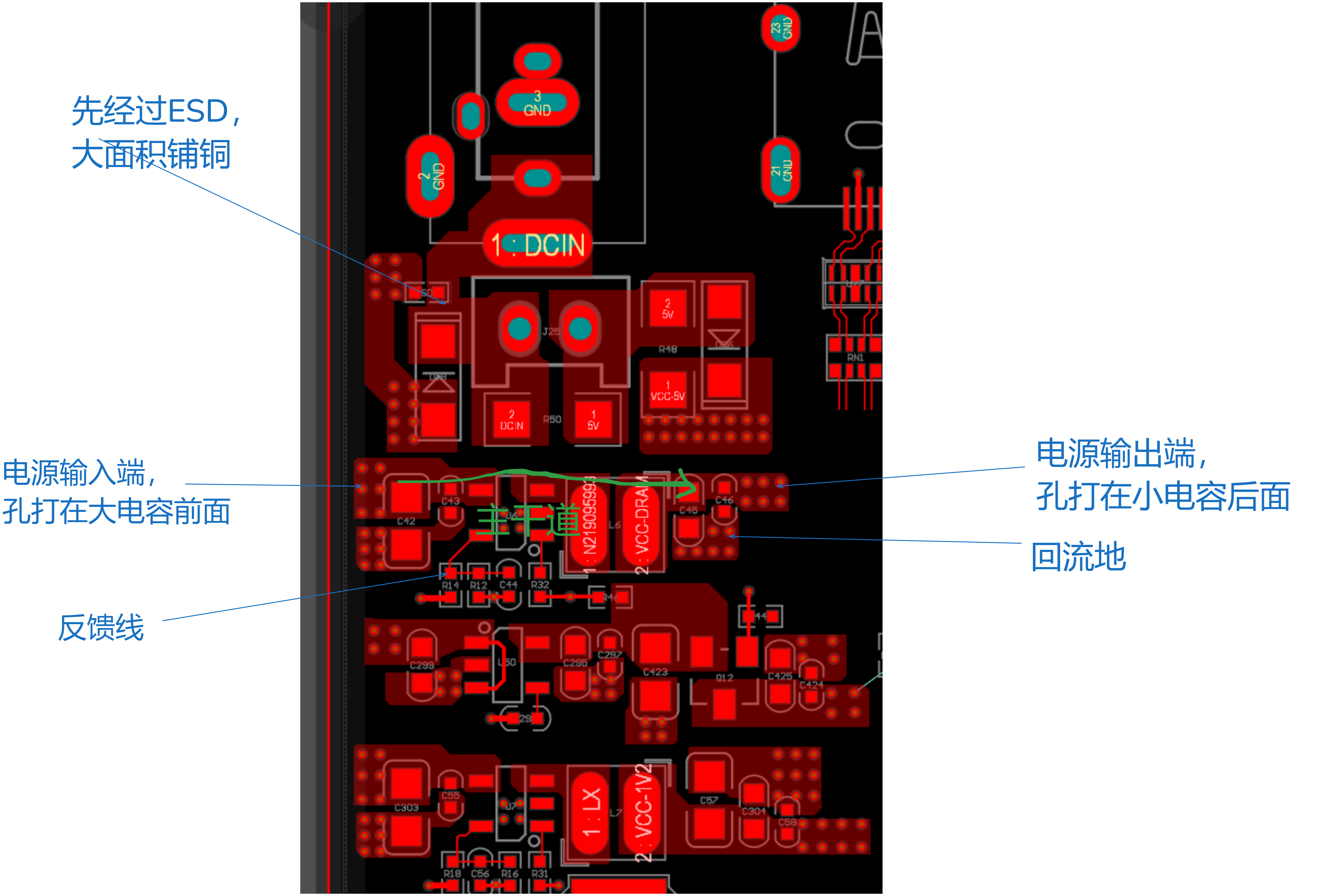

电源注意事项:

电源处理,经验:表层20mil过1A,内层40mil过1A

- 反馈取电从小电容输出端接。

- 铺铜较多,找出主干道,铺铜

- 反馈不需要加粗,使能直接连

- 主要就是输入输出的主干道宽度的大小,其他的走一根常规的信号走线,注意回流地铺铜打孔。

- 芯片的回流地,输入的打多少过孔,回流地就打多少。

- 梳理好电源走线规划,对于比较分散的电源,可以考虑作为POWER层整版电源。其他的电源先绘制好大概线路。

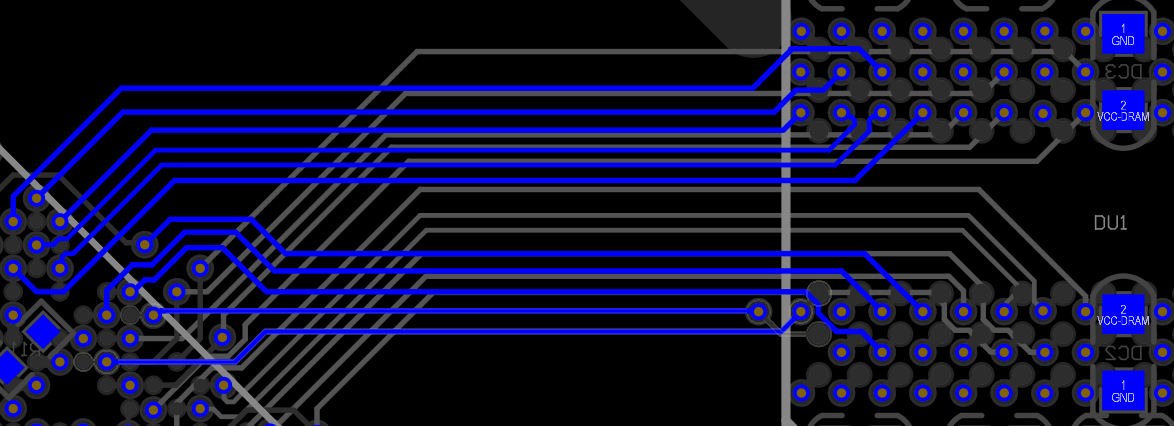

DDR布线注意事项:

- 分类,挑出电源和数据,电源和地分为A组,数据(DQ数据信号,DQS数据锁存信号,DM数据掩码信号)分为B组,其他的分为C组(地址,控制,时钟)。

- 数据分为低八位和高八位16跟,(D0-D7,LDM,LDQS),(D8-D15,UDM,UDQS)。对于DDR2,DQS为差分,变成11跟为一组。

- 数据线每10跟尽量走在同一层(D0-D7,LDM,LDQS),(D8-D15,UDM,UDQS)。

- 信号线间距满足3W原则,数据线和地址(控制)线,时钟线之间的距离保持20mil以上或至少3W。

- 空间允许条件下,应该在走线之间加一根地线进行隔离,地线宽度推荐为15-30mil

- VREF电源走线先经过电容在进入管脚,走线宽度不小于20mil,与同层其他信号线之间间距最好20mil以上

- 所有信号线都不得跨分割,且有完整的参考平面,换层时,如果改变了参考层,要注意考虑增加回流地过孔或退藕电容。

- 两片以上的DDR布线拓扑结构优选远端分支,T点的过孔打在两片DDR中间;

- 特性阻抗,单端50Ω,差分100Ω。

布数据线线时可以采用自动布线,然后自己修改线,做到节约时间。

构造T点时,要留有绕等长的空间。空间不够,可以考虑换层,移孔。单片DDR不需要构造T点。

BGA拉出走线时,位置不够的话需要修改之前的数据线,没有强制的同组同层要求。

其他注意事项:

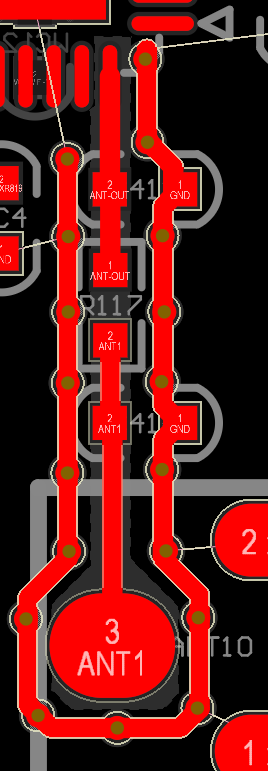

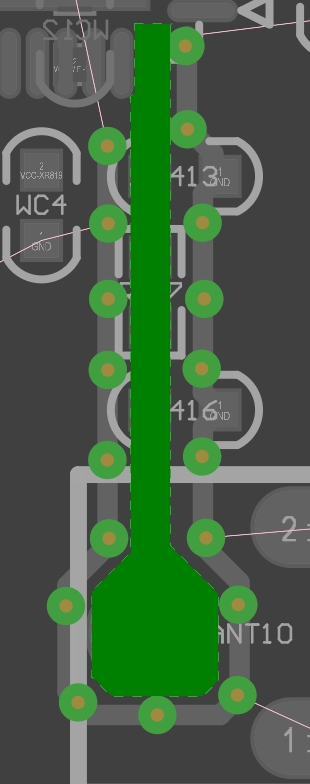

电感,晶体,天线下方不走线。走线时,采取总线方式走线,然后慢慢修线。

USB输入电源进行铺铜,注意先流过大电容,然后小电容。输入端打多少个过孔,输出端就几个。

RJ45除了差分和两个LED,其他的尽量宽度走到15-20mil。

20mil过1A电流。过孔:0.5mm过1A电流,所以根据电流来选择打孔多少,比如过孔是0.25mm,过1A打两个孔。输入端打孔打在电容旁边,输出端打孔打在电容后面。

AV音频:一字型走线。属于模拟线,走12mil。需要包地处理。

晶体采取π形摆放,走类差分线,外围立体包地。

射频天线:短线连接,50Ω阻抗设置,走12-15mil,立体包地处理。

但是为了阻抗,可以挖掉第二层的GND,Top与第三层相连,阻抗增大,功率天线,隔层参考。

3 软件篇

准备自己修改uboot和linux内核,进行开发。

静待更新。